# ADwin-light-16

## **Manual**

## For any questions, please don't hesitate to contact us:

Hotline: +49 6251 96320

Fax: +49 6251 5 68 19

E-Mail: info@ADwin.de

Internet www.ADwin.de

Jäger Computergesteuerte Messtechnik GmbH Rheinstraße 2-4 D-64653 Lorsch Germany

## **Table of contents**

| Typographical Conventions                                                                                                                       | V              |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1 Information about this manual                                                                                                                 | 1              |

| 2 System description                                                                                                                            | 2              |

| 3 Operating Environment                                                                                                                         | 7              |

| 4 Start-up of the Hardware                                                                                                                      | 8              |

| 5 Inputs and Outputs 5.1 Analog Inputs and Outputs 5.2 Digital Inputs and Outputs 5.3 Impulse/Event Counter. 5.4 LS Bus 5.5 Time-critical tasks | 11<br>13<br>14 |

| 6 Calibration                                                                                                                                   |                |

| 7 CO1 Counter Add-On                                                                                                                            | 23             |

| 8 DIO1 Add-On 8.1 Digital Inputs and Outputs 8.2 Counters. 8.3 CAN-Bus 8.4 SSI Decoder.                                                         | 28<br>29       |

| 9 DIO2 / DIO3 Add-On 9.1 Digital Inputs and Outputs 9.2 Counters. 9.3 SSI Decoder.                                                              | 43             |

| 10 PWM1 Add-On                                                                                                                                  | 54             |

| 11 ADwin-light-16-Boot                                                                                                                          | 57             |

| 12 Accessories                                                                                                                                  | 58             |

| 13 Software  13.1 Example Program  13.2 Analog Inputs and Outputs  13.3 Digital Inputs and Outputs  13.4 Counter                                | 59<br>63       |

| 13.5 CAN interface                                                                                                                              |                |

|   | 13.6 SSI interface                        | 135              |

|---|-------------------------------------------|------------------|

| Α | nnex                                      |                  |

|   | A.1 Technical Data                        |                  |

|   | A.2 Hardware Addresses - General Overview | A-7              |

|   | A.3 Hardware-Revisions                    | A-8              |

|   | A.4 RoHS Declaration of Conformity        | A-8              |

|   | A.5 Overview Connectors / Enclosures      | A-9              |

|   | A.6 Baud rates for CAN bus                | <del>\</del> -16 |

|   | A.7 Table of figures                      | ۹-19             |

|   | A.8 Index                                 | <del>۱-20</del>  |

## **Typographical Conventions**

"Warning" stands for information, which indicate damages of hardware or software, test setup or injury to persons caused by incorrect handling.

You find a "note" next to

- information, which absolutely have to be considered in order to guarantee an error free operation.

- advice for efficient operation.

"Information" refers to further information in this documentation or to other sources such as manuals, data sheets, literature, etc.

File names and paths are placed in <angle brackets> and characterized in the font Courier New.

Program commands and user inputs are characterized by the font  ${\tt Courier}$   ${\tt New}.$

Source code elements such as commands, variables, comments and other text are characterized by the font Courier New and are printed in color.

Bits in data (here: 16 bit) are referred to as follows:

| Bit No.   | 15              | 14              | 13              |   | 01                | 00                |

|-----------|-----------------|-----------------|-----------------|---|-------------------|-------------------|

| Bit value | 2 <sup>15</sup> | 2 <sup>14</sup> | 2 <sup>13</sup> |   | 2 <sup>1</sup> =2 | 2 <sup>0</sup> =1 |

| Synonym   | MSB             | -               | -               | - | -                 | LSB               |

<C:\ADwin\ ...>

Program text

Var\_1

## 1 Information about this manual

This manual contains comprehensive information about the operation of the *ADwin-light-16* system. Additional information is available in

- the manual "ADwin Driver Installation", which describes all interface installations for the ADwin systems.

Commence your installation with the help of this manual.

- the description of the configuration program ADconfig. With it, you initialize the communication of the corresponding interface with ADwin-light-16.

- the manual ADbasic, which contains all instructions for the compiler ADbasic and explains the principle of ADwin systems in particular.

The online help of *ADbasic* contains the same information.

- the description of the driver installation and command instructions for all well known development environments.

- the manual "ADwin HSM-24V", a module on the LS bus.

#### Please note:

For *ADwin* systems to function correctly, adhere strictly to the information provided in this documentation and in other mentioned manuals.

Programming, start-up and operation, as well as the modification of program parameters must be performed only by appropriately qualified personnel.

Qualified personnel are persons who, due to their education, experience and training as well as their knowledge of applicable technical standards, guidelines, accident prevention regulations and operating conditions, have been authorized by a quality assurance representative at the site to perform the necessary acivities, while recognizing and avoiding any possible dangers.

(Definition of qualified personnel as per VDE 105 and ICE 364).

This product documentation and all documents referred to, have always to be available and to be strictly observed. For damages caused by disregarding the information in this documentation or in all other additional documentations, no liability is assumed by the company *Jäger Computergesteuerte Messtechnik GmbH*, Lorsch, Germany.

This documentation, including all pictures is protected by copyright. Reproduction, translation as well as electronical and photographical archiving and modification require a written permission by the company *Jäger Computergesteuerte Messtechnik GmbH*, Lorsch, Germany.

OEM products are mentioned without referring to possible patent rights, the existence of which, may not be excluded.

Hotline address: see inner side of cover page.

Qualified personnel

Availability of the documents

Legal information

Subject to change.

## 2 System description

## 2.1 *ADwin* system concept

**ADwin** systems guarantee fast and accurate operation of measurement data acquisition and automation tasks under real-time conditions. This offers an ideal basis for applications such as:

- very fast digital closed-loop control systems

- very fast open-loop control systems

- data acquisition with very fast online analysis of the measurement data

- monitoring of complex trigger conditions and many more

**ADwin** systems are optimized for processes which need **very short process cycle times** of one millisecond down to some microseconds.

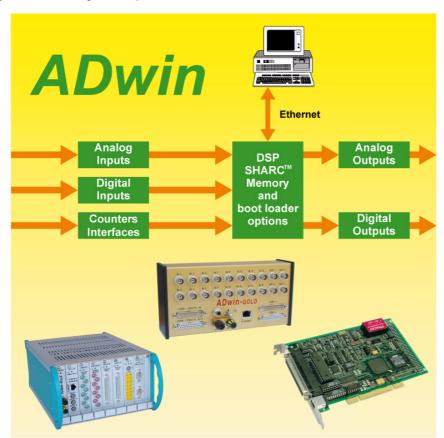

The **ADwin** system is equipped with analog and digital inputs and outputs, a fast processor (32-bit floating point signal processor) and local memory. The processor is responsible for the whole real-time processing in the system. The applications run **independent** of the PC and its workload.

The processor of the *ADwin* system processes *each* measurement value at once.

In one cycle you can acquire the status of the inputs, process the status with the help of any mathematical functions, and react to the results, even at very fast process cycle times of some microseconds. This results in a perfect and logical work sharing: The PC executes a program for visualizing of data, for input and operation of the processes, togeher with access to networks and data bases, while the processor of the **ADwin** system executes all tasks which require real-time processing concurrently.

The operating system for the DSP of the *ADwin* system has been optimized to achieve the fastest response times possible. It manages parallel processes in a *multitasking* environment. Low priority processes are managed by time slicing. Specified high priority processes interrupt all low priority processes and are immediately and completely executed (preemptive multitasking). High priority processes are executed as time-controlled or event-controlled processes (external trigger).

The built-in **timer** is responsible for the precise scheduling of high priority processes. It has a resolution of 25 nanoseconds (3,3ns since processor T11). The *ADwin* systems are characterized by an extremely short response time of only 300 nanoseconds during the change from a low to a high priority process. A continously running communication process enables a continous data exchange between the *ADwin* system and the PC even while applications are active. The communication has no influence on the real-time capability of the *ADwin* system, even so, it is possible to exchange data at any time.

The real-time development tool *ADbasic* gives the opportunity to create time-critical programs for *ADwin* systems very easily and quickly. *ADbasic* is an **integrated development environment** under Windows with possibilities of online debugging. The familiar, easy-to-learn BASIC instruction syntax has been extended by many more functions, in order to allow direct access to inputs and outputs as well as by functions for process control and communication with the PC.

System features

**Processor**

Real-time operating system

Timing

**ADbasic**

#### Communication between ADwin system and PC

The *ADwin* system is connected to the PC via an **USB or Ethernet** interface. After power-up the *ADwin* system is booted from the PC via this interface. Afterwards the *ADwin* operating system is waiting for instructions from the PC which it will process.

There are two kinds of instructions: On the one hand instructions, which transfer data from the PC to the *ADwin* system, for instance "load process", "start process" or "set parameter", on the other hand instructions which wait for a response from the *ADwin* system, for instance "read variables" or "read data sets". Both kinds of instructions are processed immediately by the *ADwin* system, which means immediate and complete responses. The *ADwin* system never sends data to the PC without request! The data transfer to the PC is always a response to an instruction coming from the PC. Thus, embedding the *ADwin* system into various programming languages and standard software packages for measurements is held simple, because they have only to be able to call functions and process the return value.

Under Windows 95/98/NT/ME/2000/XP/Vista you can use a **DLL** and an **ActiveX** interface. On this basis the following drivers for **development environments** are available:

.NET, Visual Basic, Visual-C, C/C++, Delphi, VBA (Excel, Access, Word), TestPoint, LabVIEW / LabWINDOWS, Agilent VEE (HP-VEE), InTouch, DIAdem, DASYLab, SciLab, MATLAB.

Versions for Linux, Mac OS and Java are available, too.

The simple, instruction-oriented communication with the **ADwin** system enables several Windows programs to access the same **ADwin** system in coordination at the same time. This is of course a great advantage when programs are being developed and installed.

Fig. 1 – Concept of the *ADwin* systems

**Interfaces**

Instruction processing

Software interfaces

#### **Processor and memory**

## 2.2 ADwin-light-16

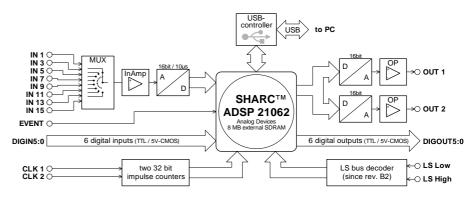

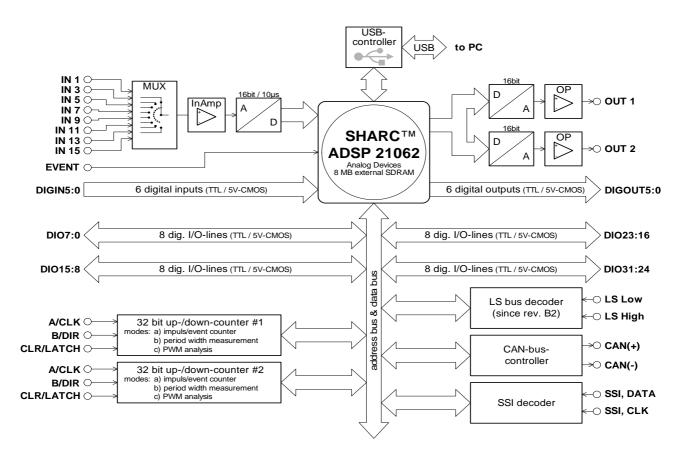

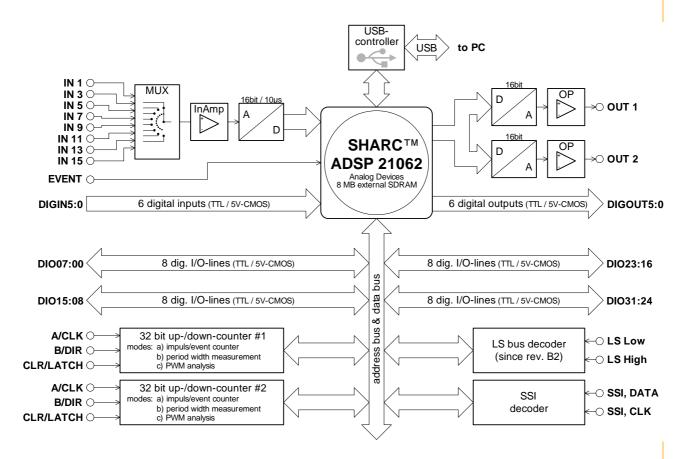

The *ADwin-light-16* system is equipped with the **32 bit signal processor** ADSP 21062 (SHARC) from Analog Devices with floating point and integer processing. It is responsible for the complete measurement data acquisition, online processing, and signal output and can instantaneously process - in combination with the A/D-converter - each measured value with sample rates of up to 100 kHz; from Rev. B an optional sample rate of 500kHz is available.

The **on-chip memory with 256 KiB** has a very short access time of 25 ns and is large enough to hold the complete *ADwin* operating system, the *ADbasic* process and all variables.

In order to get maximum access speed, all inputs and outputs are memory mapped in the external memory section of the DSP. For buffering larger quantities of data the DSP uses an **external memory** (SDRAM) of **8 MiB** (Rev. B has 16MiB).

#### **Analog inputs**

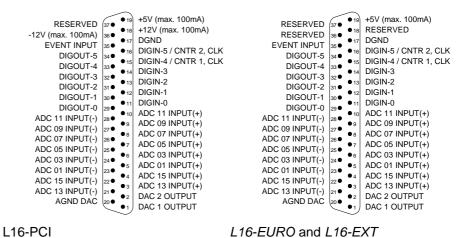

In a 37-pin D-SUB socket there are **8 analog inputs** available, which are connected to a multiplexer, whose output signal is converted with a 16 bit analog-to-digital converter (ADC, see figure below). Since revision B a sequential control for automatic conversion of several channels is available.

Fig. 2 – Functional diagram (with USB interface)

#### **Analog outputs**

*ADwin-light-16* is equipped with **2 analog outputs** with 16 bit resolution and an output voltage range of -10 V ... +10 V. The output voltages of all DACs are synchronized and calibrated per software. In order to smooth the output signal, it passes through a low pass filter with a cut-off frequency of  $f_{\rm c}=700$  kHz.

#### Digital inputs and outputs

**6 digital inputs and 6 digital outputs** are available on the 37-pin D-SUB socket. The inputs and outputs are TTL-compatible. Furthermore, there are inputs for 2 counters with 32 bit each.

#### **Trigger input**

ADwin-light-16 is equipped with a trigger input (EVENT, see also chapter 5.2 "Digital Inputs and Outputs"). Thus, processes can be triggered by a signal (trigger) and completely processed at once (see ADbasic manual, chapter "Processes in the ADwin Operating System").

A serial interface (LS bus from Rev. B2, see page 16) enables the connection of upt o 15 additional modules.

#### Scope of delivery

The standard scope of delivery for ADwin-light-16:

- ADwin-light-16 system

- USB or Ethernet connecting cable, length 1.8 m

- ADwin-CD-ROM

- Manual "Driver Installation"

- this hardware manual

**Variants**

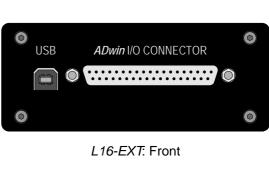

Additional items supplied with the type with external enclosure (L16-EXT) are:

- Power adapter: a PC slot plate with power supply socket and PC-internal three-pole connecting cable

- power supply cable for connection between the slot plate and L16-EXT.

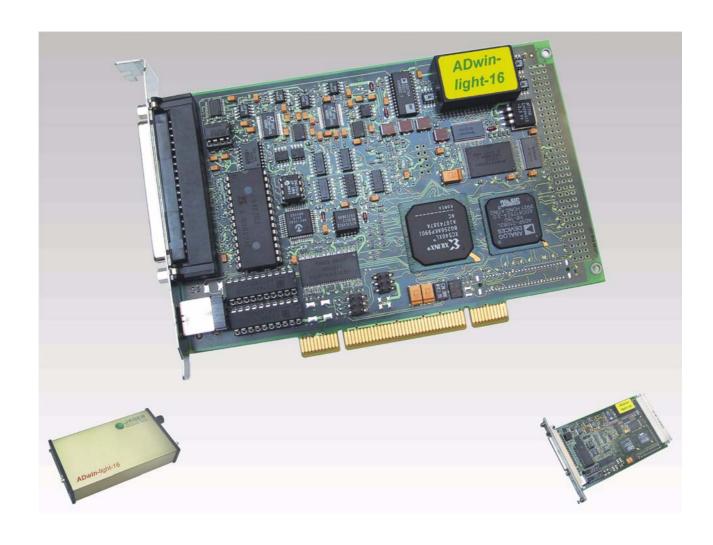

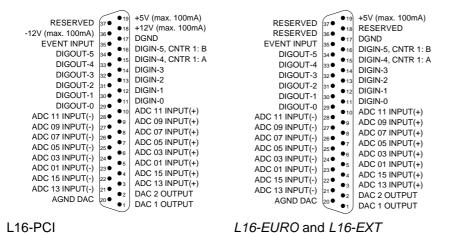

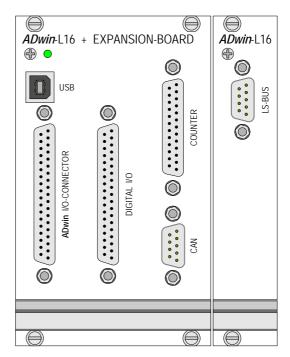

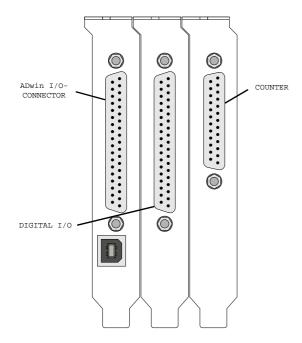

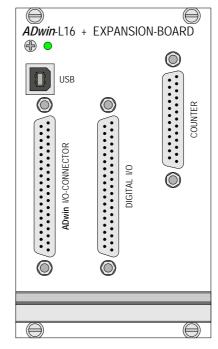

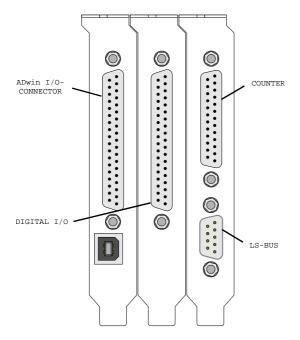

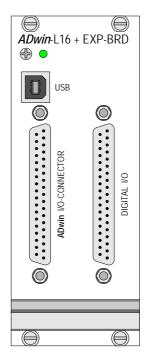

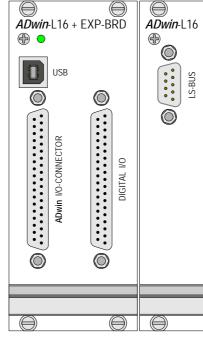

ADwin-light-16 is available as basic version with USB connection in several variants.

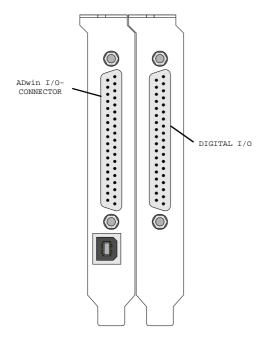

PC plug-in board (L16-PCI)

19" plug-in board (L16-EURO)

external enclosure (L16-EXT)

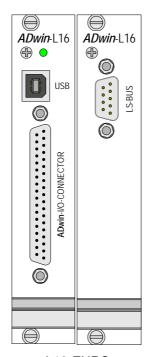

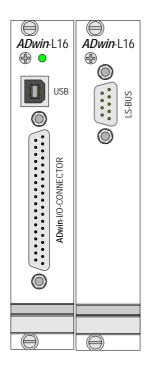

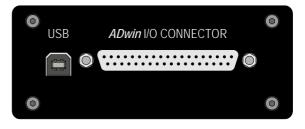

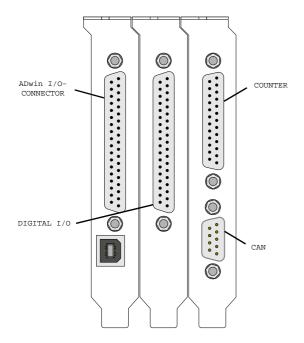

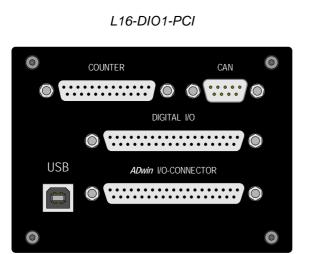

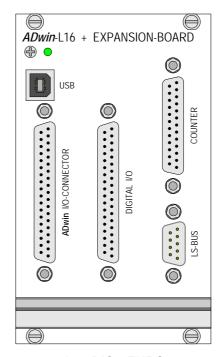

Fig. 3 - Variants

The variants L16-EURO and L16-EXT can optionally be delivered with USB or 10/100 MBit Ethernet interface. The available types of the ADwin-light-16 basic version are described in the following table.

| Туре                     | Interface |               |  |  |  |  |  |  |  |

|--------------------------|-----------|---------------|--|--|--|--|--|--|--|

|                          | USB       | Ethernet      |  |  |  |  |  |  |  |

| PC plug-in board         | L16-PCI   | _             |  |  |  |  |  |  |  |

| 19" plug-in board (Euro) | L16-EURO  | L16-EURO-ENET |  |  |  |  |  |  |  |

| External enclosure       | L16-EXT   | L16-EXT-ENET  |  |  |  |  |  |  |  |

Fig. 4 – Types of the ADwin-light-16 basic version

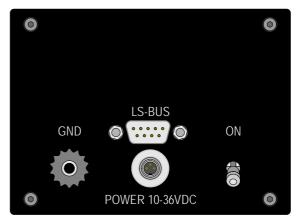

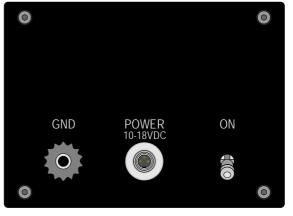

Please take into account that the power supply for the different variants varies:

- +5 Volt for L16-PCI and L16-EURO

- +10 ... +18 Volt for *L16-EXT*, since Rev. B +10 ... +36 Volt

#### 2.2.1 Ordering options (later upgrade not possible)

ADwin-light-16 can be equipped with the following options:

- L16-CO1: counter option (description see page 23) with a 32-bit up/down counter with four edge evaluation for incremental encoders.

- L16-DIO1: add-on module (description see page 25) with

- 32 digital inputs/outputs (programmable in groups of 8)

- one SSI decoder (since Rev. B)

- CAN interface (high speed; low speed as an alternative)

- two 32 bit up/down counters for impulse, period duration and duty cycle measurements as well as a four edge evaluation for the connection of incremental encoders.

- L16-DIO2: add-on module (description see page 41) with

- 32 digital input/outputs (programmable in groups of 8).

- one SSI decoder

- two 32 Bit up/down counters for impulse, period duration and duty cycle measurements as well as a four edge evaluation for incremental encoders.

- L16-DIO3: add-on module description see page 41) contains

32 digital inputs/outputs (programmable in groups of 8).

- L16-PWM1: Software add-on (description see page 53) cointains 1

PWM output and 1 SPI interface (Master).

- L16-Boot: Flash-EPROM bootloader for stand alone operation without a PC (description see page 57). May only be ordered in combination with an Ethernet interface.

- L16-Mount: Kit for installation of an L16-EXT system on a DIN top-hat rail in an electrical control cabinet with isolated mountings.

Please take into account, that the counters of the add-on boards are not additionally available, but that they replace the counters of the basic version. Therefore you cannot use the counters of different add-ons at the same time.

#### 2.2.2 Accessories

The following equipment for *ADwin-light-16* is available as accessory; description see page 58:

- ADbasic, real-time development tool for all ADwin systems

- cable connectors for an external power supply (for L16-EXT only)

- external power supply ADwin-light-16-pow (necessary for notebook operation)

#### **ADbasic**

## 3 Operating Environment

The board of the *ADwin-light-16* may only be operated in a closed casing (already given with *L16-EXT* variant).

According to type and accessories (see chapter 2.2.1f, delivery options / accessories) the system can be operated in 19" enclosures, control cabinets or as a mobile system (e.g. in vehicels).

The ADwin-light-16 system must be earth-protected, in order to

- build a ground reference point for the electronic

- conduct interferencing energy to earth.

Connect the GND socket, which is internally connected with the ground reference point and the enclosure, via a short low-impedance solid-type cable to the central earth connection point of your installation.

The types with USB interface have a galvanic connection to the PC via USB and possibly also via power supply.

The types with Ethernet interface have their data lines galvanically isolated, but the ground potentials are connected, because the shielding of the Ethernet connector (RJ-45) is connected with GND.

Transient currents, which are conducted via the enclosure or the shielding, have influence on the measured signal.

If you want to prevent transient currents, please make sure that the shielding is fully operative. Take measures for bleeding off interference, such as earthing the shielding close to the entry into the control cabinet. The more frequently you earth the shielding on its way to the machine the better the shielding will operate.

Use cables with shielding on both ends for **signal lines.** Here too, you should reduce the bleeding off of interferences via the enclosure by using screen clips.

The *ADwin-light-16* system is internally operated with a voltage of +5 V and ±15 V against GND and thus is not life-threatening. For operation with an external power supply, the instructions of the manufacturer apply.

*ADwin-light-16* is designed for operation in dry rooms. The installation environment (PC or 19" rack) may have an ambient temperature within the range +5 ... +50 °C, and a relative humidity of 0 ... 80 % (none condensing, see also Annex).

The temperature of the casing (surface temperature) of the type *L16-EXT* must not exceed +55 °C, even under extreme operating conditions - e.g. in an electrical control cabinet or if the system is exposed to the sun for longer periods of time. Otherwise, you risk damage to the device or the output of undefined data (values) which can cause damages to your measurement equipment under unfavorable circumstances.

**Galvanic connection**

Excluding transient currents

Protective extra low voltage

Ambient temperature

Chassis temperature

Reliable power supply

## 4 Start-up of the Hardware

Do not connect any signal cables to *ADwin-light-16* **on start-up** before taking the **following steps**:

- 1. Software installation / hardware installation in the PC or 19" rack. Follow the instructions in the manual: "*ADwin* Driver Installation".

- 2. Set the operating environment as described in chapter 3.

- 3. Read chapter 5 "Inputs and Outputs" in this manual.

- 4. Only now connect the signal lines to the inputs and outputs.

#### **Notes**

Avoid direct contact with uninsulated parts in order to protect them against electrostatic discharges.

Please pay attention that a reliable power source is used.

For standard version, this concerns the PC, and otherwise the external power supply, or if operated in a vehicle, the battery voltage.

If using current-limiting power supplies, please pay attention the current demand at power-up which can be a multiple of the operating current. Detailed information is contained in the Technical Data (Annex).

**In case of power failure** all unsaved data are lost. Undefined data could cause damage to your equipment under unfavorable circumstances.

#### **Check Data Communication**

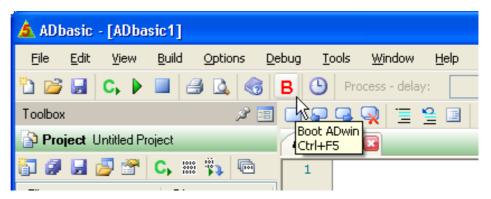

Start *ADbasic* and boot the *ADwin* system by clicking the boot button **B**.

The display in the status line: "ADwin is booted" shows that the operating system has been loaded appropriately and that *ADbasic* can establish a connection to the *ADwin* system.

Programming the *ADwin* systems is described in more detail in the *ADbasic* manual.

Start with the programming examples in the *ADbasic* Tutorial.

#### ADbasic programs

## 5 Inputs and Outputs

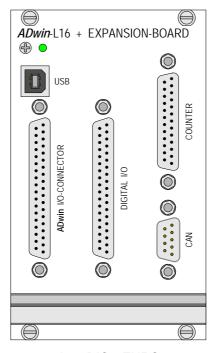

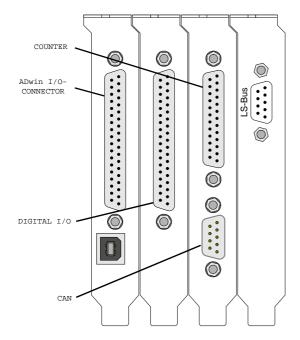

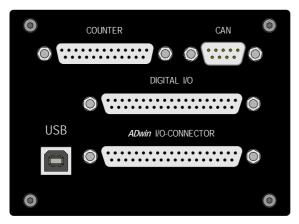

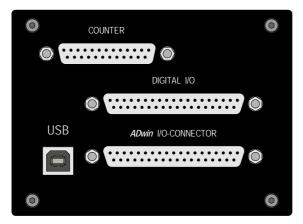

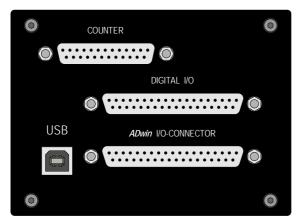

The *ADwin-light-16* system has the following connectors (pin assignment see next page):

- connector for USB or Ethernet

- 37-pin D-SUB socket ADwin I/O CONNECTOR for

- · 8 analog inputs

- · 2 analog outputs

- · 6 each, digital inputs and outputs

- 1 digital trigger input

- · 2 impulse/event counters with 32 bit

- Output for power supply +5V; L16-PCI also ±12V

- 9-pin D-SUB socket LS-BUS for the LS bus interface (since Rev. B2).

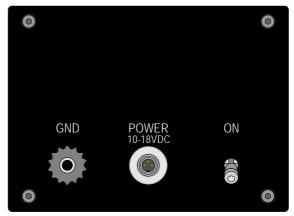

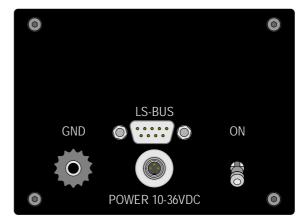

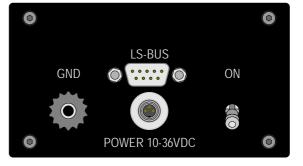

The variant *L16-EXT* has an additional GND socket (see earth protection, page 7), a power input socket and a manual on/off switch.

All inputs and outputs may only be operated according to the specifications given (see Annex A-1: Technical Data). In case of doubt, ask the manufacturer of the equipment to which you intend to connect the *ADwin-light-16* system with.

Open inputs can cause errors – above all in an environment which is not free of any interferences. For your own safety, connect unused inputs as close as possible to the D-SUB socket on a defined level (e.g. GND). Separate these inputs from open circuit lines.

Exception to this is the event input, which already has an internal pull-up resistor (10  $k\Omega$ ).

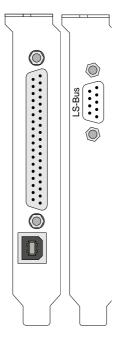

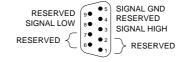

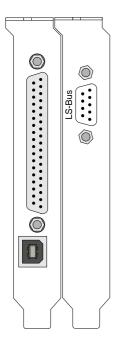

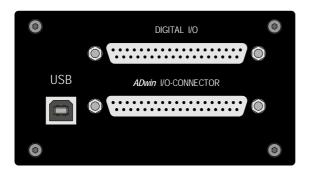

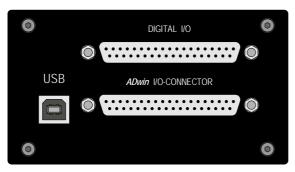

L16-PCI

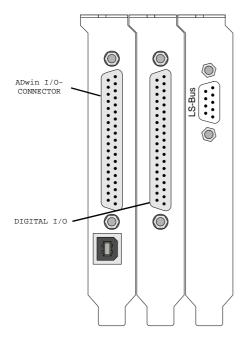

L16-EURO

GND ON ON POWER 10-36VDC

L16-EXT: Back

Fig. 5 – Connectors *ADwin-light-16*

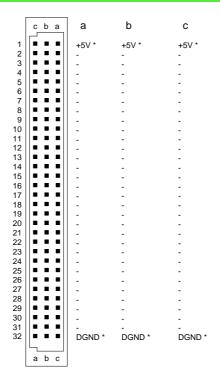

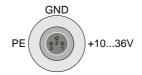

Fig. 6 – *L16-EURO* VG96 connector for power supply (female)

Fig. 7 – *L16-EXT* power connector (male)

Fig. 8 – Pin assignment LS-BUS (female)

Fig. 9 – Pin assignment inputs/outputs (female)

For fast and easy programming there are standard instructions available in the compiler *ADbasic*, which enable a user to easily measure or output data (see also *ADbasic* manual). Use other instructions (such as direct register access) only if extremely time-critical or special tasks require to do so. (see also chapter 13).

More detailed information about the analog as well as the digital inputs and outputs can be found in the following chapters.

#### 5.1 Analog Inputs and Outputs

The variant *L16-EXT* has to be earth-protected, in order to perform measurements without interference. For this, connect the GND socket via a low impedance solid-type cable to the central earth connection point of your installation. When using the variants PCI or EURO, the earth protection is made via PC or the 19" rack.

For *L16-EXT*, the enclosure is connected to the protective earth conductor of the PC via the GND-line of the power supply cable as well as via the GND-line of the USB cable.

#### 5.1.1 Analog Inputs

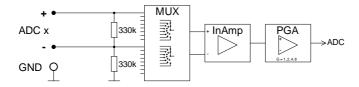

The system has 8 analog measurement inputs, which are connected through a multiplexer to the 16-bit analog-to-digital converter (ADC). The multiplexer settling time is 6.5 µs with a full scale range of 20 V.

The inputs are all odd-numbered (ADC 01, ADC 03, ... ADC 15), which has to be considered during programming.

The analog inputs are differential. For each of the measurement channels there is a positive and a negative input, between which the voltage difference is measured (pay attention to the potential of the input lines).

Please note, that the inputs do need a mass connection between the system's GND and the signal source. This is in addition to the connections to the positive and negative input.

Fig. 10 - Input circuitry of an analog input

The signal at the multiplexer output is converted by a 16-bit analog-to-digital converter (ADC); see Fig. 2 – Functional diagram (with USB interface). The conversion time is  $10\mu s$  (since Rev. B selectable per software:  $2\mu s$ ) at a resolution of 305  $\mu V$ .

The instruction ADC ( ) executes a complete measurement with an ADC on one analog input. Thus, this instruction considers for instance the settling time of the multiplexer and assures perfect measurements (see also *ADbasic* manual).

From Rev. B the signals of several selected analog inputs can be converted (sequentially) with a single instruction. The inputs are selected with <code>Seq\_Init</code>, conversion is started with <code>Start\_Conv</code> and results are read with <code>Seq\_Read</code>.

#### Standard instructions

Earth protection

Multiplexer

Differential

16-bit measurement

Complete measurement

Rev. B with sequential control

#### **DAC** instruction

Voltage range

Allocation of digits and voltage

#### 5.1.2 Analog Outputs

The standard instruction **DAC** (number, value) checks each of the values exceeding or falling below of the 16-bit value range. If the value is in the 16-bit value range, the indicated value is output on the output number. If it is not, the maximum or minimum value is output (see also *ADbasic* manual).

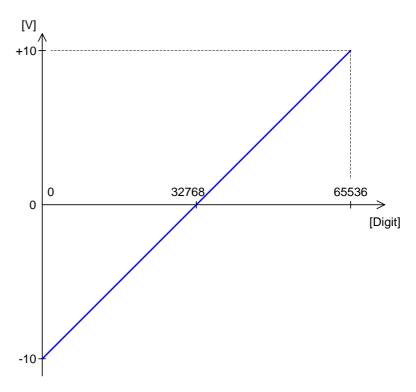

#### 5.1.3 Calculation Basis

The voltage range of the *ADwin-light-16* system at the analog inputs and outputs is -10 V to +10 V (bipolar 10 V).

The 65536 (2<sup>16</sup>) digits are allocated to the corresponding voltage ranges of the ADCs and DACs insofar that

- 0 (zero) digits correspond to the maximum negative voltage and

- 65535 digits correspond to the maximum positive voltage

The value for 65,536 digits, exactly 10 Volt, is just outside the measurement range, so that there is a maximum voltage value of 9.999695 Volt for the 16-bit conversion.

Fig. 11 – Zero offset in the standard setting of bipolar 10 Volt

Bipolar range leads to a zero offset which is shown below.

For the voltage range of  $-10 \text{ V} \dots +10 \text{ V}$  applies  $\text{U}_{\text{OFF}} = -10 \text{ V}$

The quantization level  $U_{LSB}$  is the smallest digitally displayable voltage difference and is equivalent to the voltage of the least significant bit (LSB). The  $U_{LSB}$  is equivalent to the formula: 20 V /  $2^{16}$  = 305.175  $\mu$ V.

The measured 16-bit value of the ADC is returned to the lower word of the binary cell. Here you must also find the DAC value to be output.

| Bit           | 3116       | 15 | 14   | 13    | 12  | 11  | 10   | 09  | 80 | 07  | 06 | 05    | 04   | 03  | 02   | 01   | 00 |

|---------------|------------|----|------|-------|-----|-----|------|-----|----|-----|----|-------|------|-----|------|------|----|

| 32-bit memory | upper word | •  | 16-k | oit v | alu | e o | f th | e A | DC | /D/ | ۱C | in th | ne I | owe | er v | vord | t  |

**Least Significant Bit**

####

For a DAC:

DAC

$$Digits = \frac{U_{OUT} - U_{OFF}}{U_{LSB}}$$

For an ADC:

ADC

$$Digits = \frac{U_{IN} - U_{OFF}}{U_{LSB}}$$

$$U_{IN} = Digits \cdot U_{LSB} + U_{OFF}$$

#### **Tolerances**

Slight deviations regarding the calculated values may be within the tolerance of the individual component. Two kinds of deviation are possible, which are indicated in this manual (in LSB):

- The integral non-linearity (INL) defines the maximum deviation from the ideal straight line of the conversion characteristics curve, covering the whole input voltage range.

- The differential non-linearity (DNL) defines the maximum deviation from the ideal quantization level.

INL

DNL

#### 5.2 Digital Inputs and Outputs

6 digital inputs (DIGIN 00 ... DIGIN 05) and 6 digital outputs (DIGOUT 00 ... DIGOUT 05) are available on the 37-pin D-SUB socket. The pin assignment be found in figure 9 on page 10.

The inputs DIGIN 04 and DIGIN 05 are used as counter inputs at the same time and may be read as digital inputs while being used as counters. This is not true when using a DIO1-add-on (see page 25) or DIO2-add-on (see page 41).

The digital inputs and outputs are TTL-compatible and not protected against overvoltage.

Do not use connections marked as "RESERVED". They are reserved for upcoming changes or expansions and can cause damages to your system if you do not pay attention to this fact.

The *ADwin-light-16* system is equipped with an external trigger input (EVENT). An external signal (trigger) with rising edge may be used to start processes, which are processed immediately and completely (see *ADbasic* manual, chapter "Structure of an *ADbasic*-Program").

The functions of the digital channels are easily programmed with *ADbasic* instructions:

| Function                              | Instruction  |

|---------------------------------------|--------------|

| Read single digital input.            | DIGIN        |

| Read all digital inputs.              | DIGIN_WORD   |

| Set all digital outputs.              | DIGOUT_WORD  |

| Set one digital output to level High. | SET_DIGOUT   |

| Set one digital output to level Low.  | CLEAR_DIGOUT |

The instructions are included in the file <code><ADWL16</code> . INC> and are described in the <code>ADbasic</code> manual and in the online help.

Digital inputs/outputs

**Trigger input (EVENT)**

**Programming**

#### 5.3 Impulse/Event Counter

The ADwin-light-16 system is equipped with 2 impulse/event counters, each with 32 bits, which may be configured or read out both together or individually.

With the options L16-CO1, L16-DIO1 or L16-DIO2 the counters described here are replaced by other counters. You will find the corresponding description in chapter 7 "CO1 Counter Add-On", chapter 8 "DIO1 Add-On" or chapter 9 "DIO2 / DIO3 Add-On".

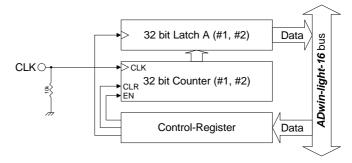

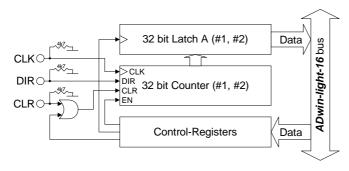

#### 5.3.1 Hardware

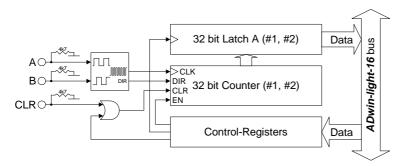

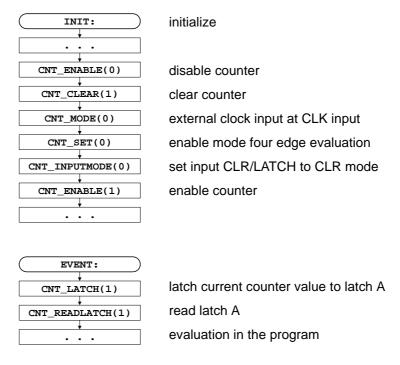

The figure shows the design of a single counter.

Fig. 12 – Block diagram of the impulse/event counter

The counters are externally clocked that means they increase their counter values by incrementing at each positive edge at the clock input (CLK). Both counters have a latch A, into which the counter value can be latched (under program control) for read out.

The counters are controlled with special *ADbasic* instructions via the control register. The instructions are described in Fig. 13 – Counter instructions - short reference (below) and in the ADbasic manual (or online help).

The clock inputs are on pins 15 and 16 (see Fig. 9 – Pin assignment inputs/outputs (female), page 10); for the correct function TTL compatible signals are

required. More details and limit values can be found in the Technical Data in the Annex. Both inputs can optionally be used as digital signal input (see also chapter 5.2).

The inputs of the impulse/event counters have pull-down resistors. Nevertheless open inputs can cause errors in an environment which is not free of interference. Therefore set unused inputs to a defined level (e.g. GND).

#### 5.3.2 Software

by the opposing function..

The counters are easily programmed using ADbasic instructions. The instructions are part of an include file which must be included at the beginning of a program: #INCLUDE ADWL16.INC

The instructions for both counters are shortly illustrated in the following table and more detailed in the ADbasic manual or online help. You can configure each counter individually or both counters together.

| Counter nº              | 2                                                                               | 1 | Comment   |  |  |  |  |  |  |  |  |  |

|-------------------------|---------------------------------------------------------------------------------|---|-----------|--|--|--|--|--|--|--|--|--|

| Bit 1 0                 |                                                                                 |   |           |  |  |  |  |  |  |  |  |  |

| <pre>Cnt_Clear( )</pre> | 0                                                                               | 0 | no effect |  |  |  |  |  |  |  |  |  |

| 1 1 clear counter*      |                                                                                 |   |           |  |  |  |  |  |  |  |  |  |

| * these functions are   | * these functions are reset after being executed. All other functions are reset |   |           |  |  |  |  |  |  |  |  |  |

Fig. 13 - Counter instructions - short reference

#### **Setting inputs**

#### Include file

| Counter no                                                                   | 2  | 1   | Comment                                             |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------|----|-----|-----------------------------------------------------|--|--|--|--|--|--|--|

| Bit                                                                          | 1  | 0   |                                                     |  |  |  |  |  |  |  |

| Cnt_Enable( )                                                                | 0  | 0   | disable counter                                     |  |  |  |  |  |  |  |

|                                                                              | 1  | 1   | enable counter (pay attention to running counters)  |  |  |  |  |  |  |  |

| Cnt_Latch( )                                                                 | 0  | 0   | no effect                                           |  |  |  |  |  |  |  |

|                                                                              | 1  | 1   | copy counter value into latch A *                   |  |  |  |  |  |  |  |

| Cnt_ReadLatch(#                                                              | :) |     | read latch A (# = counter-n <sup>o</sup> 1, 2)      |  |  |  |  |  |  |  |

| Cnt_Read(#) copy counter value into latch A and read it (# = counter nº1, 2) |    |     |                                                     |  |  |  |  |  |  |  |

| * these functions are                                                        | re | set | after being executed. All other functions are reset |  |  |  |  |  |  |  |

Fig. 13 - Counter instructions - short reference

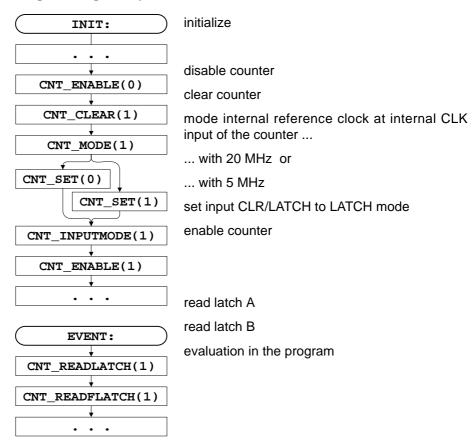

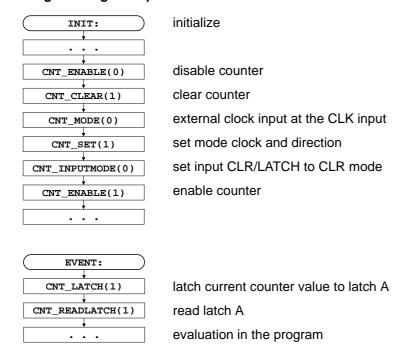

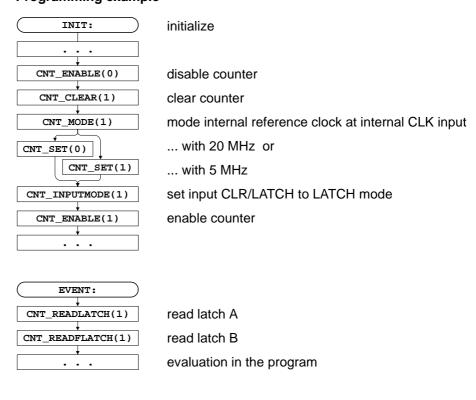

Please configure the counters in the following sequence:

1. disable specified counter (Cnt\_Enable)

The instruction <code>Cnt\_Enable</code> always accesses all counters. Even if the status (disabled/enabled) of only one counter shall be changed, also those counters must be configured whose status shall remain unchanged.

clear counter (Cnt\_Clear)

by the opposing function..

3. enable counter (Cnt\_Enable)

For further processing of the counter value in the *ADbasic* program, transfer the value into latch A and read it from there.

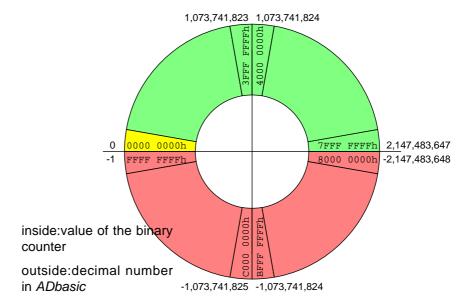

#### 5.3.3 Evaluation of the counter contents

The binary counters generate 32 bit values. Distinguish clearly between the evaluation of these binary values (e.g. differences) and the screen representation as decimal numbers.

To correctly evaluate the counter contents you need its original 32 bit values, especially with calculating differences. This is guaranteed only by use of *ADbasic* variables of type **Long**.

The representation of 32 bit values in *ADbasic* often leads to confusion, because the signless counter value is shown as signed decimal number (see circle below). Consequently a transition between positive and negative range of numbers is shown on the screen, which has no influence upon the evaluation of the counter contents.

For the sake of completeness the following describes the interpretation of a binary value:

The most significant bit (MSB) is interpreted as sign.

With a positive sign, the following 31 bits are directly interpreted as numerical value; binary and decimal value are similar.

With a negative sign, the 31 bits are first inverted, one added, and then interpreted as numerical value (2's complement); thus, negative decimal numbers have an absolute value different to the corresponding binary value.

Calculate differences only with integer numbers (LONG).

For programming please remember that an "lap overflow" between the read out of two counts - i.e. the current counter value "laps" the last counter value which has been read - is not registered.

Sequence of instructions

unchanged bit pattern

"Lap overflow"

Circle

Such a lap overflow occurs after some 3½ minutes with an input frequency of 20 MHz or after more than 14 minutes with 5 MHz.

Fig. 14 – Circle model for interpretation of counter values

#### **5.4 LS Bus**

ADwin-light-16 provides an interface for LS bus on a 9-pin DSub connector (female); the pin assignement is shown on page 10.

The LS bus is a bi-directional serial bus with 5MHz clock rate (Low Speed). The bus is a in-house-design to access external modules. The first module available is HSM-24V which can process 24 Volt signals on 32 digital channels.

The bus is set up as line connection, i.e. the *ADwin* interface and up to 15 LS bus modules are connected to each other via two-way links. The last module of the LS bus must have the bus termination activated. The maximum bus length is 5 m.

The LS bus modules are programmed with *ADbasic* instructions, which are sent from the LS bus interface of the *ADwin* system. The instructions are mostly specific for the module and are described in the manual of the LS bus module (or in the online help).

The variants L16-PCI and L16-Euro have the DSub connector on a separate cover plate. If the LS bus is not used, the connecting cable may be pulled from from the main board and the cover removed.

Please note for reconnecting to have the connector socket pick up all 10 pins of the on-board plug and to not have the cable twisted.

#### 5.5 Time-critical tasks

For extremely time-critical tasks instructions may be used which allow direct access to control and data registers of the hardware (see *ADbasic* manual or online help). These registers are to be found in the memory address area of the ADSP (memory mapped). These instructions also allow optimization of the program structure.

Contrary to the standard instructions ADC() and DAC() the instructions for direct access do not have any test routines. Before using them, good knowlegde is required about programming and time and function sequences in an analog-to-digital converter, because this kind programming is closely related to the hardware.

#### Analog inputs and outputs

Execute the following *ADbasic* instructions instead of the standard instruction **ADC**() according to the following order:

```

Set_Mux()

... 'wait for settling time

Start_Conv()

Wait_EOC() 'wait for end of conversion

ReadADC()

```

It is important to set a sufficient time-delay using additional programming instructions between the instructions <code>Start\_Conv()</code> and <code>Set\_Mux()</code>, in order to account for multiplexer settling time (see also *ADbasic* manual: "Instruction Reference").

Use the waiting times shown below for instance for computing operations and thus, save computing time:

- $-\,$  Settling time of the multiplexer: At a maximum voltage jump of 20 V it is 6.5  $\mu s.$

- Conversion time of the 16 bit ADC: 10 μs; since Rev. B: 2μs optional.

#### Hardware addresses of the control and data registers

Using the instructions **Peek** and **Poke** (see *ADbasic* manual or online help) you can directly access the control and data registers. This may accelerate the processing of the program, e.g.:

- a measurement can be executed very quickly.

- you can write very quickly into one or more DAC registers, and the output may be synchronously started.

Please ensure that the calculated analog outputs values are within the range limits.

Time-critical tasks

ADC()

Program structure

ADC DAC

The hardware addresses of the registers may be found in the following tables, grouped as analog inputs, analog outputs, digital inputs/outputs and counters.

Please take into account that some registers have an influence on several processes.

| Address     | Function                                         | Bit nº |       |   |   |   |   |   |   |   |   |   |   | Comment                                                    |

|-------------|--------------------------------------------------|--------|-------|---|---|---|---|---|---|---|---|---|---|------------------------------------------------------------|

| [HEX]       |                                                  | 31-16  | 15-10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |                                                            |

| 20 40 00 00 | set multiplexer to input channel (ADC 01 ADC 15) | -      | -     | - | - | - | - | 0 | 0 | 0 | n | n | n | "nnn" binary = 07 decimal;<br>selected channel = nnn*2 + 1 |

| 20 40 00 10 | start conversion: ADC#1                          | -      | -     | - | - | - | - | - | 1 | 1 | 1 | 1 | S | s = 0 : start conversion<br>s = 1 : no effect              |

| 20 40 00 20 | conversion status(EOC): ADC#1                    | -      | -     | - | - | - | - | - | - | - | - | - | _ | e = 0 :end conversion<br>e = 1 : conversion is running     |

| 20 40 00 30 | read register: ADC#1                             | -      | Х     | Х | Х | Х | Х | Х | Х | Х | Х | Х | х |                                                            |

| 20 40 01 00 | read register and start conversion:<br>ADC#1     | _      | х     | х | х | х | х | х | х | х | х | х |   | x : result of the conversion                               |

Fig. 15 – ADC hardware addresses of the control and data registers

| Address     | Function                                                       | Bit nº |       |   |   |   |   |   |   |   |   |   |    | Comment                                       |

|-------------|----------------------------------------------------------------|--------|-------|---|---|---|---|---|---|---|---|---|----|-----------------------------------------------|

| [HEX]       |                                                                | 31-16  | 15-10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |                                               |

| 20 40 00 10 | start conversion: all DAC synchro-<br>nously                   | -      | -     | - | - | - | - | - | 1 | 1 | s | 1 | 11 | s = 0 : start conversion<br>s = 1 : no effect |

| 20 40 00 50 | write only to the register: DAC #1                             | -      | х     | Х | Х | Х | Х | Х | Х | Х | Х | Х | х  |                                               |

| 20 40 00 60 | write only to the register: DAC #2                             | -      | х     | Х | Х | Х | Х | Х | Х | Х | Х | Х | х  |                                               |

| 20 40 02 00 | write to the register and start conversion immediately: DAC #1 | -      | х     | х | х | х | х | х | х | х | х | х | х  | x : digital value to be converted             |

| 20 40 02 10 | write to the register and start conversion immediately: DAC #2 | -      | х     | х | х | х | х | х | х | х | х | х | х  |                                               |

Fig. 16 – DAC hardware addresses of the control and data registers

| Address     | Function                            | Bit nº |      |   |   |   |   |   |   | Comment                        |

|-------------|-------------------------------------|--------|------|---|---|---|---|---|---|--------------------------------|

| [HEX]       |                                     | 31:16  | 15:6 | 5 | 4 | 3 | 2 | 1 | 0 |                                |

| 20 40 00 B0 | input register DIGIN-05DIGIN-00     | -      | -    | х | х | Х | Х | х | Х | x : digital value read in      |

| 20 40 00 C0 | output register DIGOUT-05 DIGOUT-00 | -      | -    | х | х | Х | х | х | х | x : digital value to be output |

| 20 40 00 C4 | DIGOUT Bit-SET-Register             | -      | -    | 0 | 0 | 0 | 0 | 0 | 0 | no effect                      |

| 20 40 00 04 | DIGGOT Bit GET Register             | -      | -    | 1 | 1 | 1 | 1 | 1 | 1 | set bit                        |

| 20.40.00.C8 | DIGOUT Bit-CLEAR-Register           | -      | -    | 0 | 0 | 0 | 0 | 0 | 0 | no effect                      |

| 20 40 00 00 | DIGGOT BIL GEEAR Register           | -      | -    | 1 | 1 | 1 | 1 | 1 | 1 | clear bit                      |

Fig. 17 – DIO hardware addresses of the control and data registers

|                                           | 31:16                                                                                       | 145.0                  |                        |                        |                        |                        |                        |                                               |                                                                          |

|-------------------------------------------|---------------------------------------------------------------------------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|-----------------------------------------------|--------------------------------------------------------------------------|

|                                           | -                                                                                           | 15:6                   | 5                      | 4                      | 3                      | 2                      | 1                      | 0                                             |                                                                          |

| A, counter #1                             | Х                                                                                           | х                      | Х                      | Х                      | х                      | х                      | х                      | Х                                             | x : latched counter value                                                |

| A, counter #2                             | Х                                                                                           | х                      | Х                      | Х                      | Х                      | х                      | Х                      | х                                             | x : latched counter value                                                |

| unter (- CNT ENABLE())                    | -                                                                                           | -                      | -                      | -                      | -                      | -                      | 0                      | 0                                             | counter disabled                                                         |

| Triable/disable counter (= CN1_ENABLE( )) | -                                                                                           | -                      | -                      | -                      | -                      | -                      | 1                      | 1                                             | counter enabled                                                          |

| TT CIEXD())                               | -                                                                                           | -                      | -                      | -                      | -                      | -                      | 0                      | 0                                             | no effect                                                                |

| (I_CLEAR())                               | -                                                                                           | -                      | -                      | -                      | -                      | -                      | 1                      | 1                                             | clear counter *                                                          |

| NT TATCU()                                | -                                                                                           | -                      | -                      | -                      | -                      | -                      | 0                      | 0                                             | no effect                                                                |

| MI_HAICH(/)                               | -                                                                                           | -                      | -                      | -                      | -                      | -                      | 1                      | 1                                             | latch counter value into latch A *                                       |

|                                           | A, counter #2  unter (= CNT_ENABLE())  NT_CLEAR())  NT_LATCH())  ction has been executed. A | unter (= CNT_ENABLE()) 0  1  NT_CLEAR()) 1  1 | unter (= CNT_ENABLE()) 0 0 1 1  NT_CLEAR()) 0 0  NT_LATCH()) 0 0  1 1  1 |

Fig. 18 – Counter hardware addresses of the control and data registers

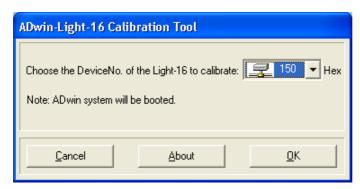

#### 6 Calibration

The two digital-to-analog (DAC) and the analog-to-digital (ADC) converter of the *ADwin* system have been calibrated in factory. In accordance with the regulations for keeping the measurement accuracy in your field of application, the systems must be calibrated in regular time intervals.

Calibration is made via software. The program <L16Calib.exe> is located in the Start folder at <Programs\ADwin\Calibration\L16Calib>.

You need the following tools for the calibration:

- a digital multimeter (DMM) with a resolution of 30 μV.

- a reference voltage source with a resolution of 30 μV. Optionally you connect DAC 1 to ADC 01(+), DAC 2 to ADC 03(+) and AGND DAC with ADC 01(-) and ADC 03(-), for instance in form of a test connector. You need these connections also for the calibration diagram.

- connection cables from the inputs/outputs to the reference voltage source and to the measurement device.

Connect your *ADwin-light-16* system with the PC and configure it with the program <ADconfig.exe>.

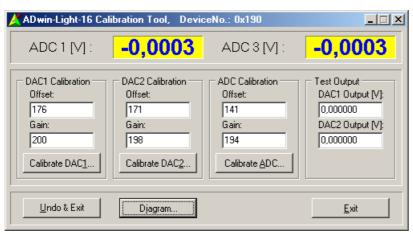

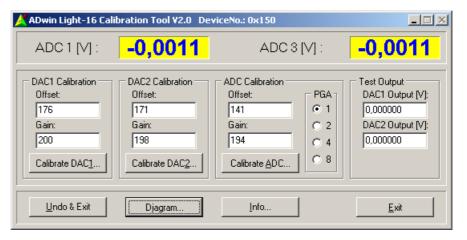

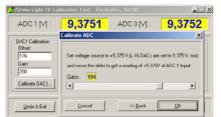

Start the calibration program <L16Calib.exe>. The window "ADwinlight-16 Calibration Tool" appears.

Select the device number of the system to be calibrated and confirm by pressing "OK".

You will get a warning, if you haven't selected an *ADwin-light-16* system or if you have selected one with an older firm ware version. You can ignore the warning with "YES" or return to the previous windows with "NO".

An **overview window** appears. In the header the selected device number is displayed.

Step 1

Step 2

The upper field shows the current measured values at the inputs ADC 01 and ADC 03. Below you will find the calibration settings for Offset and Gain of both DACs and the ADC; there you can directly enter values. You start calibration of the relevant converter with "Calibrate ..."

At the right side ("Test Output") you can enter voltage values in the fields DAC1 and DAC2, which will automatically be output on the corresponding outputs.

For Revision B the overview window has additional items: The PGA field so set the gain value and the Info button to show some version information of the device.

All settings you have made are automatically saved.

In the lower line you can undo all inputs with "Undo & Exit" and leave the calibration program. "Diagram" displays in a graph the accuracy of the current calibration setting. If you leave the program with "Exit" all settings remain.

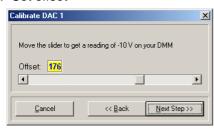

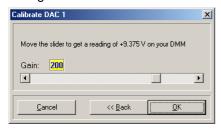

Calibrate the converters in the order you like (only with reference voltage source). The calibration of a converter is effected in 3 steps; you can switch between the windows of the steps by using the forward/backward buttons. Calibration is also possible without reference voltage source, but it will not be so precise. Calibrate first the DAC1 and DAC2, and then the ADC.

The 3 levels for calibrating a converter are described below, for the DAC in the left column and for the ADC in the right column.

1. Connect the external device (DMM/voltage source) Select the corresponding key "Calibrate ..." for calibrating a converter; the first window appears.:

Connect a DMM with the pins Connect the voltage source (or a AGND DAC and DAC1 or DAC2.

DAC output) with the inputs ADC 01 or ADC 03.

Please note Fig. 9 – Pin assignment inputs/outputs (female). Select "Next Step >>".

Step 3

#### 2. Set offset

bar in such a manner that your digital multimeter displays -10 V.

Adjust the offset value at the scroll- Set your voltage source to 0 V (setpoint). The setting of the ADC to this value is made automatically.

> Adjust the offset value at the scrollbar in such a manner that the setpoint at the ADC 01 is displayed in the overview window.

> With Rev. B all settings of this step are done automatically.

Select "Next Step >>".

#### 3. Set gain

Adjust the offset value at the scrollbar in such a manner that your digital multimeter displays -10 V.

Set your voltage source to 9,375 V (setpoint). The setting of the ADC to this value is made automatically. Adjust the offset value at the scrollbar in such a manner that the setpoint at the ADC 01 is displayed in the overview window.

With Rev. B all settings of this step are done automatically.

The calibration for this converter has finished. Select "OK". Repeat step 3 for the other converters if necessary.

#### Step 4

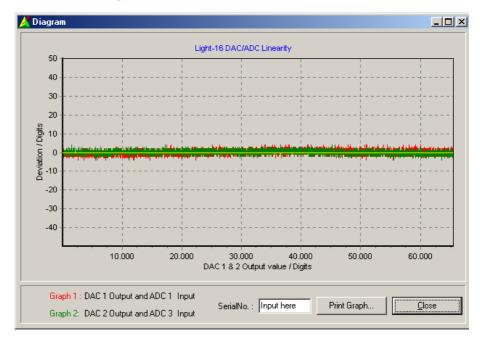

With a diagram (button Diagram in the overview window) you can check the accuracy of the calibration.

Connect first the output DAC 1 with the input ADC 01 as well as the output DAC 2 with the input ADC 03.

The program outputs the values 0...65,535 digits on both DACs, compares them to the measured input values and displays the deviation in graphs. Graph 1 (red) for DAC 1 / ADC 01 and graph 2 (green) for DAC 2 / ADC 03. The deviation should be smaller than 5 digits.

You can print the graph with Print Graph (a color printer is recommended). To do so, enter the serial number of your *ADwin* system, so that you can allocate the printout later. On the printout you will also find the calibration settings and the date of print.

With Close you return to the overview window.

The calibration is finished.

Step 5

### 7 CO1 Counter Add-On

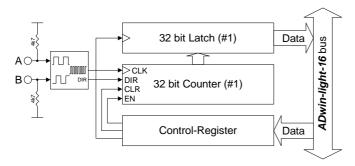

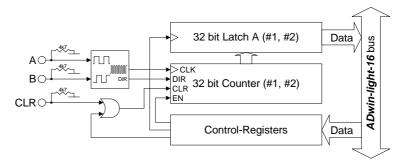

The counter add-on CO1 (option L16-CO1) provides a 32-bit up/down counter with four edge evaluation and replaces the counter of the basic version (Fig. 19 – Block diagram of the L16-CO1 counter add-on shows the design of the counter).

Fig. 19 – Block diagram of the *L16-CO1* counter add-on

#### 7.1 Hardware

The counter is **externally clocked** and has a four edge evaluation for the connection of an encoder. The counter is read out via latch A, the control is made with **ADbasic** instructions via a control register (see "CO1 instructions, short reference" on page 24).

The four edge evaluation converts the digital input signals A and B (which are 90 degrees off-phase) into a clock (CLK) and direction signal (DIR) for the counter. Here a clock signal is generated from each edge of the A and B signals. The count direction (DIR) is determined by the order of the rising and falling edges of these signals.

The clock inputs A and B are on the pins 15 and 16 of the D-SUB socket (see pin assignment below); TTL-compatible signals are necessary for the correct function. More details and limit values can be found in the Technical Data in the Annex.

Both inputs can be used optionally as digital signal input (see also chapter 5.2).

Although all inputs of the CO1 add-on have a pull-down resistor, open-ended inputs can cause errors in an environment which is not free of interferences. Therefore set unused inputs on a defined level (e.g. GND).

Fig. 20 - Pin assignment of L16-CO1

**Setting inputs**

#### Include file

## 7.2 Programming

The CO1 add-on is easily programmed by using *ADbasic* instructions. The instructions are part of an include file which must be included at the beginning of a program:

**#Include** ADWL16.INC

The instructions for the CO1 add-on are shortly illustrated in the following table and more detailed in the *ADbasic* manual or online help.

| Counter nº                                                                                                         | 1 | Comment                                                                                  |

|--------------------------------------------------------------------------------------------------------------------|---|------------------------------------------------------------------------------------------|

| Bit                                                                                                                | 0 |                                                                                          |

| Cnt_Clear( )                                                                                                       | 0 | no effect                                                                                |

|                                                                                                                    | 1 | clear counter*                                                                           |

| Cnt_Enable( )                                                                                                      | 0 | disable counter                                                                          |

|                                                                                                                    | 1 | enable counter (pay attention to running counters)                                       |

| Cnt_Latch( )                                                                                                       | 0 | no effect                                                                                |

|                                                                                                                    | 1 | copy counter value into latch A *                                                        |

| Cnt_ReadLatch(#)                                                                                                   |   | read latch A (# = counter nº 1)                                                          |

| <pre>Cnt_Read(#)</pre>                                                                                             |   | copy counter value into latch A and read it $(\# = \text{counter } n^{\underline{o}} 1)$ |

| * The bits are reset after the function has been executed. All other functions are reset by the opposing function. |   |                                                                                          |

Fig. 21 – CO1 instructions, short reference

Please evaluate the counter contents only with variables of type **Integer** or **Long**, above all when you want to evaluate differences or the count direction (see also page 15).

The count direction (up/down) can reliably be derived from the

**sign of the difference:** [new counter value] minus [old counter value] and not from the *comparison* of the counter values.

For extremely time-critical tasks you can use instructions with which you have direct access to control and data registers of the counter. In the table the corresponding hardware addresses are illustrated.

The hardware addresses of the CO1 counters are identical with or replace those of the basic counter version.

| Address<br>[HEX] Function               |                                 | Bit number |                 | Comment                                            |

|-----------------------------------------|---------------------------------|------------|-----------------|----------------------------------------------------|

|                                         |                                 | 31:01      | 00              | Comment                                            |

| 20 40 02 04                             | contents of latch A, counter #1 | х          | х               | x : latched counter value                          |

| 20 40 03 00 enable counter CNT_ENABLE() | -                               | 0          | disable counter |                                                    |

|                                         | CNT_ENABLE()                    | -          | 1               | enable counter (pay attention to running counters) |

| 20 40 03 10 clear counter CNT_CLEAR()   | -                               | 0          | no effecft      |                                                    |

|                                         | CNT_CLEAR()                     | -          | 1               | clear counter*                                     |

| 120 40 03 20 1                          | latch counter CNT_LATCH()       | -          | 0               | no effect                                          |

|                                         |                                 | -          | 1               | latch counter*                                     |

|                                         |                                 |            |                 |                                                    |

<sup>\*</sup> The bits are reset after the function has been executed. All other functions are reset by the opposing function.

Fig. 22 – CO1 hardware addresses of the control and data registers

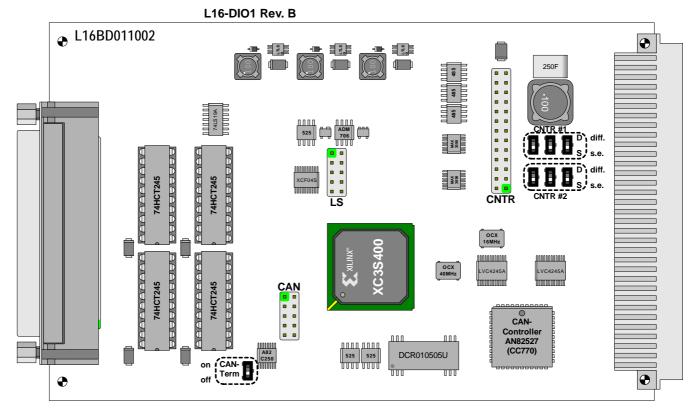

#### 8 DIO1 Add-On

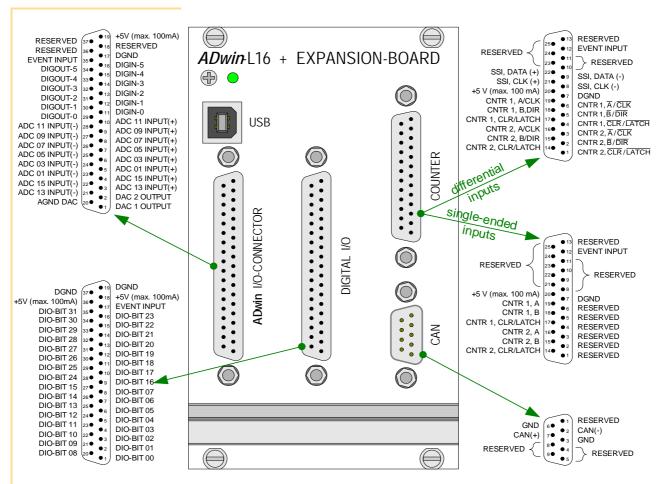

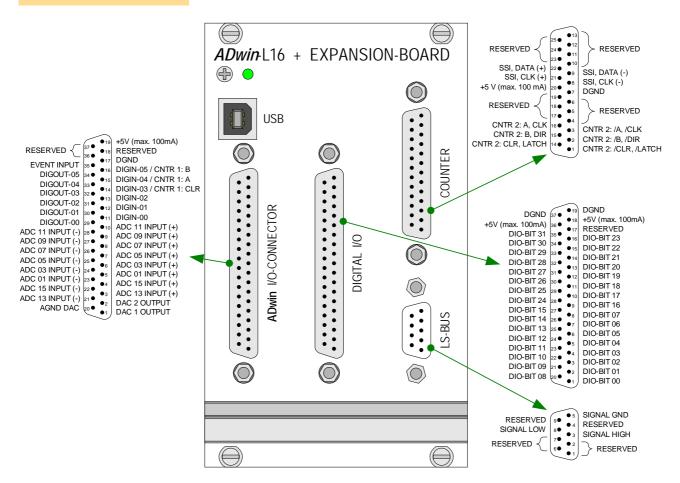

With the DIO1 add-on you are additionally provided with:

- 32 digital inputs/outputs (programmable in groups of 8), page 28

- 2 counters, page 29: 32 bit up/down counters for impulse, period duration and duty cycle measurements as well as a four edge evaluation for connection of incremental encoders.

Inputs can be set to single-ended or differential via DIP siwtches.

The counters of the basic version are replaced by the DIO1 counters.

- CAN interface (high-speed), page 36

- 1 SSI decoder (page 40), since Rev. B.

The SSI decoder enables the connection of an incremental encoder with SSI interface. The inputs are available on the COUNTER socket, the signals are differential and have RS422/485 levels (5V).

The block diagram shows the basic functions of an L16 system with the additional functions of the DIO1 add-on (as USB version).

Fig. 23 – Block diagram of *L16-DIO1* (with USB interface)

The pin assignment at the connection "*ADwin* I/O-CONNECTOR" is similar to the basic version, except one difference: The pins 15/16 - in the basic version each with double functions - are now solely used as DIGIN-04 and DIGIN-05.

The pin assignment of the LS bus interface is shown on page 10.

Fig. 24 – Overview of the *L16-EURO-DIO1* with pin assignments For other L16 variants, the plugs are named identical.

#### **Hardware configuration**

There are several DIP switches on the DIO1 board, with which you can change the settings for the counters and the CAN interface.

The setting can only be made when the board is not installed or when the casing is opened. Please pay attention to the safety instructions at the beginning of this documentation.

| variant   | How to proceed                                                                                                                                                                                                                                                                          |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L16-EURO, | Deinstalling the printed circuit board (PCB)                                                                                                                                                                                                                                            |

| L16-PCI   | The deinstallation of the board is made in reverse order to the installation, which is described in the manual " <b>ADwin</b> Driver Installation".                                                                                                                                     |

| L16-EXT   | Opening the casing                                                                                                                                                                                                                                                                      |

|           | You open the casing by unscrewing the upper Allen screws (2 mm) at both sides and loosening the lower screws. Slope the side plates and pull off the upper part of the casing. Note the orientation of the casing for the reinstallation. You are now looking directly on the DIO1 PCB. |

Reassambling is made in reverse order.

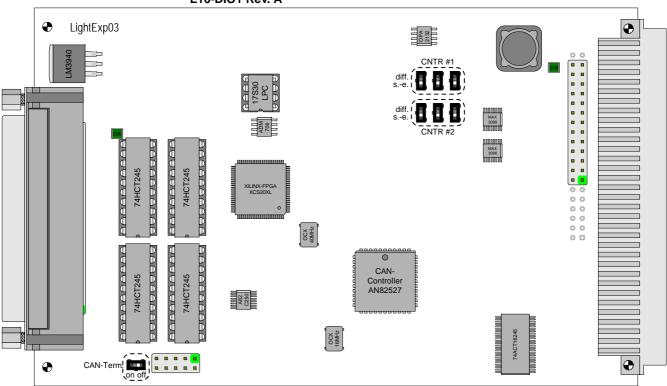

**Position of DIP switches**

The exact position of the DIP switches is shown in the following figure (pay attention to the revision). The dotted frame shows the allocation of the DIP switches to the counters 1 and 2 (upper half, half at right) and to the CAN interface (lower left corner).

Counters 1 and 2: For differential mode set all 3 DIP switches of the corresponding counter into upward position (direction see also fig. 25); for single-ended operation set the switches into downward position.

CAN interface: If a termination is necessary, set the DIP switch to the top (L16 Rev. B) or toward the CAN connector (L16 Rev. A).

Fig. 25 - Position of the DIP switches on the DIO1 PCB

**Trigger input**

Find more information on setting of the DIP switches in chapter 8.2 "Counters" and chapter 8.3 "CAN-Bus".

The technical data of the DIO1 add-on is shown in the Annex.

#### 8.1 Digital Inputs and Outputs

In addition to the digital inputs/outputs of the basic version (DIGIN, DIGOUT, EVENT), you have 32 digital inputs or outputs (abbrev. DIO) on the 37-pin D-SUB socket "Digital I/O". They are programmable in groups of 8 each as inputs or outputs.

With an external signal (trigger) at the event input a process can be triggered, and can be processed immediately and completely (see *ADbasic* manual, chapter: "Structure of an *ADbasic* program").

The digital inputs are TTL compatible and are not protected against overvoltage.

**Power-up configuration**

After power-up all connections are configured as inputs; this corresponds to the instruction Conf\_DIO\_E(0). With the instruction

Conf\_DIO\_E(n)

You program the 32 DIO lines in 4 groups with 8 lines each as input or output (see online help). The following table shows the 16 possible configurations you will get with this instruction. In order to use this instruction you have to include the file <adwl16.inc>.

| Conf_DIO_E(n)                | DIO 31 DIO 24                                                     | DIO 23 DIO 16 | DIO 15 DIO 08                                              | DIO 07 DIO 00 |

|------------------------------|-------------------------------------------------------------------|---------------|------------------------------------------------------------|---------------|

| 0                            | IN                                                                | IN            | IN                                                         | IN            |

| 1                            | IN                                                                | IN            | IN                                                         | OUT           |

| 2                            | IN                                                                | IN            | OUT                                                        | IN            |

| 3                            | IN                                                                | IN            | OUT                                                        | OUT           |

| 4                            | IN                                                                | OUT           | IN                                                         | IN            |

| 5                            | IN                                                                | OUT           | IN                                                         | OUT           |

| 6                            | IN                                                                | OUT           | OUT                                                        | IN            |

| 7                            | IN                                                                | OUT           | OUT                                                        | OUT           |

| 8                            | OUT                                                               | IN            | IN                                                         | IN            |

| 9                            | OUT                                                               | IN            | IN                                                         | OUT           |

| 10                           | OUT                                                               | IN            | OUT                                                        | IN            |

| 11                           | OUT                                                               | IN            | OUT                                                        | OUT           |

| 12                           | OUT                                                               | OUT           | IN                                                         | IN            |

| 13                           | OUT                                                               | OUT           | IN                                                         | OUT           |

| 14                           | OUT                                                               | OUT           | OUT                                                        | IN            |

| 15                           | OUT                                                               | OUT           | OUT                                                        | OUT           |

| ADbasic instructions to use: | Digin_Word2_E<br>Digout_Word2_I<br>Digout_Set2_E<br>Digout_Reset2 |               | Digin_Word1_E Digout_Word1_E Digout_Set1_E Digout_Reset1_E |               |

Fig. 26 – Configurations with Conf\_DIO\_E

More information about programming of time-critical tasks can be found in chapter 5.5 on page 17.

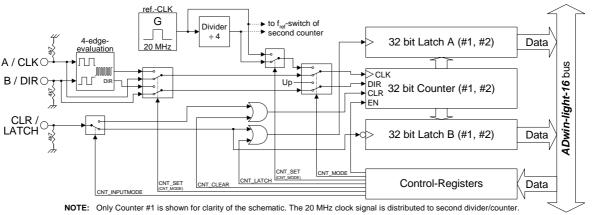

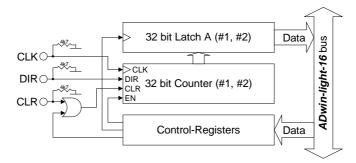

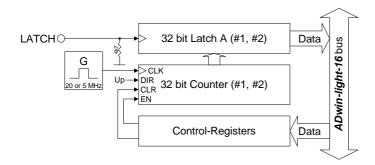

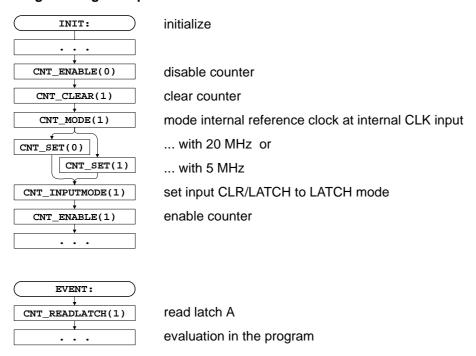

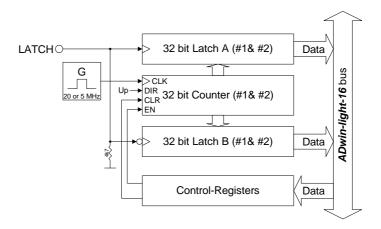

#### 8.2 Counters

The add-on DIO1 provides **two 32-bit counters**, which you can configure and read out individually or all together. You can transfer single-ended or differential signals to the inputs; operating mode to be set via DIP switches, see below. The counters replace the incremental counters of the basic version.

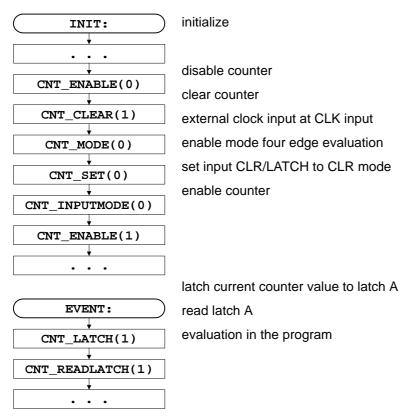

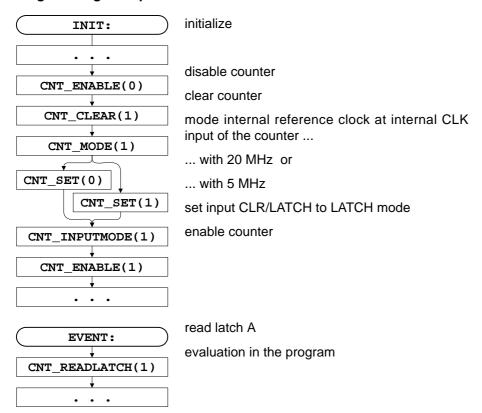

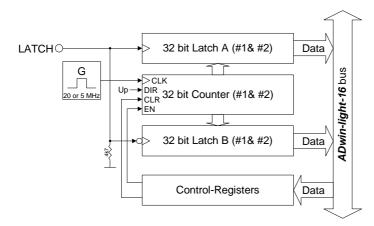

The counters can be **internally or externally clocked** and are read out via accompanying latches. All counters have a latch A as well as a latch B (the figure shows the design of a single counter).

The counter values can be cleared or transferred into a latch by using programming instructions or (at special configurations) when there is an external signal at CLR/LATCH.

Counter

Latch

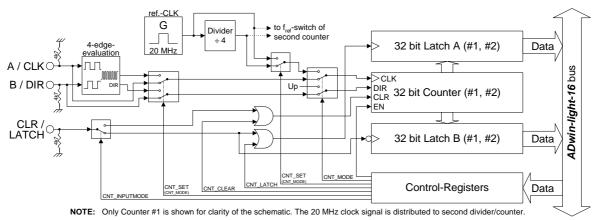

Fig. 27 - Block diagram of DIO1 counter

There are the following operating modes: event counting (external clock) and pulse width measurement (internal clock), see also chapter 8.2.2 / 8.2.3:

4. Event counting: Incrementing/decrementing of the counter is caused by external square-wave signals at the inputs A/CLK and B/DIR. A signal at CLR/LATCH either sets the counter to zero (CLR) or has the counter value written into the latch (LATCH).

There are the modes:

- Clock and direction: Every positive edge at CLK increments or drecrements the counter value by one. The signal at DIR determines the counting direction (0 = down, 1 = up).

- Four edge evaluation: Every edge of the signals (off-phase by 90 degrees) at A/CLK and B/DIR causes the counter to increment/decrement. The counting direction is determined by the sequence of the rising/falling edges of these signals. This mode is particularly used for incremental encoders.

- 5. Pulse width measurement: Incrementing/decrementing of the counter is caused by an internal reference clock with a signal frequency of 20 MHz (optionally 5 MHz after scaler). The square-wave signal at CLR/LATCH is evaluated: With every positive edge of the input signal the counter value is written to latch A, with a negative edge to latch B.

You can calculate:

- the period duration of the input signal at CLR/LATCH from the values in latch A and latch B.

- the impulse width and pause time from the values in latch A and latch B.

External clocking

Internal clock

#### Selecting the operating mode of the counter inputs

You can use the counter inputs in single-ended or differential mode. The setting is not fixed upon delivery. Therefore set the operating mode at the DIP switches of the DIO1 printed circuit board (position of DIP switches see fig. 25).

For differential mode set all 3 DIP switches of the corresponding counter into upward position (direction see also fig. 25); for single-ended operation set the switches into downward position.

#### 8.2.1 Programming

The DIO1 counters are easily programmed by using *ADbasic* instructions. The instructions are part of an include file which must be included at the beginning of a program:

**#Include** ADWL16.INC

The instructions for the DIO1 counters are shortly illustrated in the following table and more detailed in the *ADbasic* manual or online help.

| Counter nº                   | 2                                                                                                                                             | 1 | Comment                                                                              |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------------------------------------------------------------------------|--|

| Bit                          | 1                                                                                                                                             | 0 |                                                                                      |  |

| <pre>Cnt_Clear( )</pre>      | 0                                                                                                                                             | 0 | no effect                                                                            |  |